# Architettura degli elaboratori

#### Matteo Lombardi

# **Indice**

- 1.0 Introduzione

- 1.1 Approccio strutturale

- 1.2 Unità di misura

- 1.3 Storia degli elaboratori

- 1.4 Tipologie di elaboratori attualmente disponibili

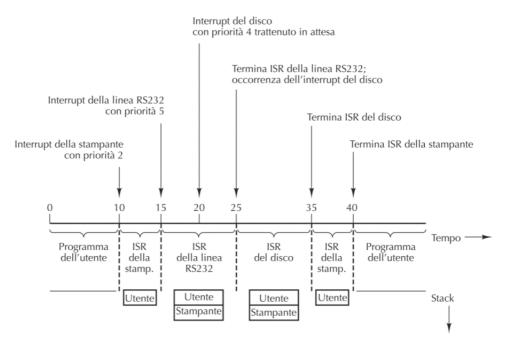

- 2.0 Organizzazione dei sistemi di calcolo

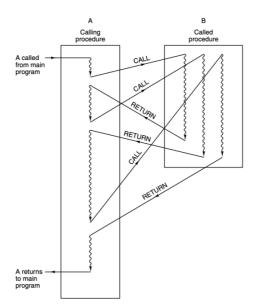

- 2.1 Processore

- 2.2 Memorie

- 2.3 Dispositivi di input e output

- 3.0 Porte logiche e circuiti combinatori

- 3.1 Algebra di Boole

- 3.2 Tabella di verità e formula canonica

- 3.3 Porte logiche

- 3.4 Mappa di Karnaugh e formula minimale

- 4.0 Rappresentazione dell'informazione

- 4.1 Numeri interi

- 4.2 Numeri con la virgola

- 4.3 Caratteri

- 4.4 Codici correttori

- 5.0 Circuiti sequenziali

- 5.1 Latch

- 5.2 Flip-Flop

- 5.3 Registri e memorie

- 6.0 Microarchitettura

- 6.1 Microarchitettura del processore Hack

- 6.2 Organizzazione delle memorie

- 6.3 Microarchitetture moderne, prefetch e pipeline

- 7.0 Livello ISA (Instruction Set Architecture)

- 7.1 IS (Instruction Set) del computer Hack

- 7.2 ISA (Instruction Set Architecture) generale

- 7.3 ISA (Instruction Set Architecture) del computer Hack

- 7.4 Assemblatore

- 7.4.1 Assemblatore del computer Hack

- 7.4.2 Programmazione in C

- 8.0 Sistema operativo

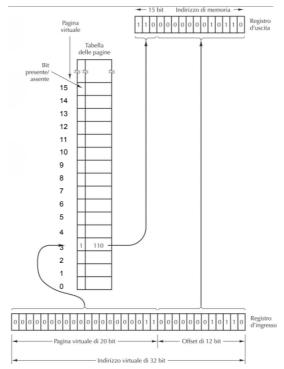

- 8.1 Paginazione

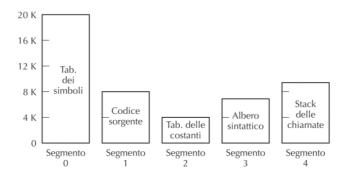

- 8.2 Segmentazione

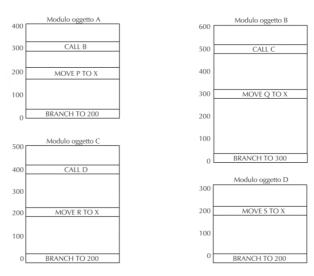

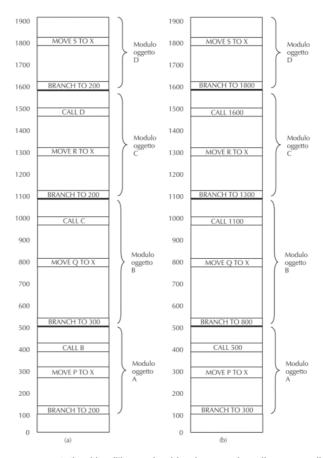

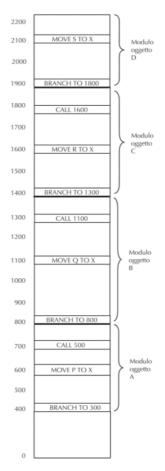

- 8.3 Collegamento di un programma

- 9.0 Virtual Machine

- 9.1 Linguaggio per virtual machine

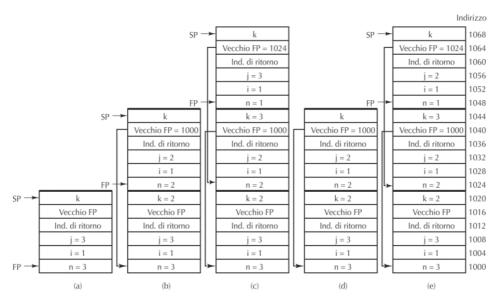

- 9.2 Modello a stack

- 9.3 Subroutine

- 10.0 Debugging

- 10.1 Errori nei programmi

- 10.2 Tecniche di debugging

# Contenuti

### ▼ 1.0 - Introduzione

L'architettura degli elaboratori consiste nello studio della progettazione delle parti di un computer visibili ai programmatori.

# **▼ 1.1 - Approccio strutturale**

# Introduzione all'approccio strutturale

Un **elaboratore** consiste in una macchina capace di effettuare operazioni eseguendo delle istruzioni che le vengono assegnate (l'insieme di queste istruzioni è detto programma).

Un elaboratore è capace di risolvere solo programmi composti da un set di istruzioni molto semplice, che corrispondono al linguaggio macchina.

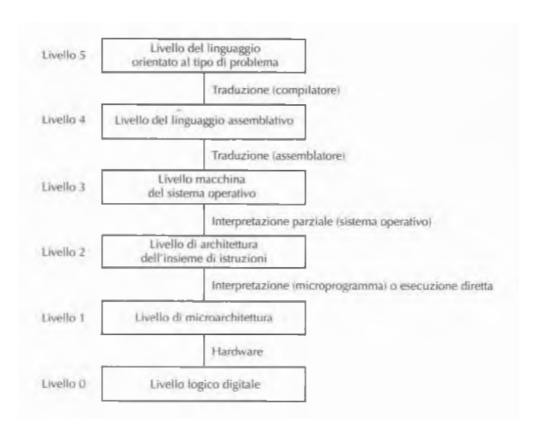

Per far eseguire ad un elaboratore un programma costituito da istruzioni molto complesse viene utilizzato un **approccio strutturale**, il quale consiste nello strutturare il calcolatore utilizzando diversi **livelli di astrazione**, ciascuno costruito a partire da quello sottostante.

A questo punto dunque sorge un problema: come far eseguire il set di istruzioni scritte in un livello più alto all'elaboratore, il quale comprende solamente istruzioni in linguaggio macchina?

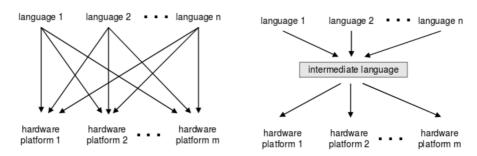

#### Traduzione

La traduzione, effettuata da un **compilatore**, consiste nell'attività di tradurre tutto il programma, passando per i livelli intermedi, in linguaggio macchina prima di essere eseguito.

# Interpretazione

L'interpretazione, effettuata da un **interprete**, consiste nel tradurre una singola istruzione del programma ed eseguirla, per poi passare a quella successiva.

### I livelli di astrazione dell'elaboratore

# · Livello 0 - Porte logiche.

Il primo livello che noi consideriamo è quello composto dalle porte logiche, tuttavia esistono dei livelli sottostanti il quale studio ricade però nell'ambito dell'elettronica e della fisica.

Le porte logiche sono infatti composte da **transistor**, i quali sono dei semiconduttori che regolano il voltaggio della corrente in modo da generare segnali elettrici. Diverse porte unite insieme permettono inoltre di formare 1 bit di informazione.

### Livello 1 - Microarchitettura.

Il livello di microarchitettura è composto da una **memoria** formata da un insieme di registri e da una **ALU (Arithmetic Logic Unit)**, la quale opera eseguendo istruzioni sui dati presenti in memoria.

Per far comunicare la ALU con la memoria è necessario un **percorso dati**, il quale può essere controllato sia lato software, tramite un microprogramma, che lato hardware.

### · Livello 2 - Livello ISA.

Rappresenta l'interfaccia tra l'hardware e il software di un elaboratore, in quanto è composto da un insieme di istruzioni eseguibili dalla microarchitettura.

# · Livello 3 e 4 - Livelli ibridi.

I livelli 3-4 sono chiamati livelli ibridi in quanto non sono nettamente separati e sono composti principalmente da:

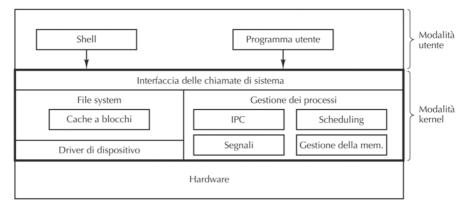

### Sistema operativo

Fornisce una serie di servizi che permettono di gestire le **risorse** (memoria, CPU, dispositivi di I/O ecc.) ed eseguire **processi**.

# • Linguaggio assemblativo

Permette di programmare per i livelli sottostanti in maniera più semplice utilizzando un linguaggio più di alto livello.

# · Livello 5 - Linguaggi di alto livello.

Il livello 5 è formato da quei linguaggi di programmazione detti "di alto livello", tra i quali troviamo C, C++, Java ecc.

#### ▼ 1.2 - Unità di misura

MIPS: milioni di operazioni per secondo

GFLOPS: miliardi di operazioni floating-point per secondo

# ▼ 1.3 - Storia degli elaboratori

### • Generazione 0 - Computer meccanici

- o 1600 Creazione delle prime macchine che permettevano di fare calcoli matematici

- 1800 Prima macchina con una struttura simile agli elaboratori moderni, la quale comprendeva:

- Magazzino (piccolo storage)

- Mulino (unità computazionale)

- Dispositivo di input (schede perforate)

- Dispositivo di output (stampa o schede perforate)

### • Generazione 1 - Computer basati su valvole

- Colossus: primo elaboratore digitale basato sull'elettromagnetismo. Venne ideato da Alan Turing al fine di decifrare i messaggi inviati dai tedeschi durante la seconda guerra mondiale.

- **Architettura di Von Neumann**, sulla quale si baseranno quasi tutti gli elaboratori che verranno utilizzati in seguito.

### • Generazione 2 - Computer basati su transistor

Creazione delle prime macchine parallele con diverse unità funzionali preposte a compiti diversi.

### • Generazione 3 - Computer basati su circuiti integrati

- Utilizzo della **multiprogrammazione**: mentre si aspetta l'input/output di un programma se ne può eseguire un altro.

- Utilizzo della microprogrammazione per emulare dei modelli precedenti di pc (utilizzato da IBM per i suoi computer)

# • Generazione 4 - Computer basati su VSLI

- VSLI (Very Large Scale Integration): possibilità di inserire una grande mole di transistor in un unico chip

- L'evoluzione nel numero di transistor presenti in un chip ha seguito la legge di Moore, secondo la quale la quantità di transistor in un chip aumenta del 60% ogni anno.

# • Generazione 5 - Computer ubiqui e invisibili

- **Computer ubiqui**: dispositivi economici ma con una grande potenza di calcolo (smartphone, tablet ecc.).

- Computer invisibili: dispositivi conosciuti per le loro funzionalità piuttosto che per le loro architetture di calcolo.

### ▼ 1.4 - Tipologie di elaboratori attualmente disponibili

Dal meno potente al più potente:

- Computer usa e getta (Qualche MIPS)

- Sistemi embedded (1 100 MIPS)

- Smartphone e tablet (10k 100k MIPS)

- Console da gioco (200 1000 GFLOPS)

- Pc (100 1000 GFLOPS)

- Server e workstation (200 GFLOPS 20 TFLOPS)

- Cluster (raggruppamento) di server (500 GFLOPS 50 TFLOPS)

# ▼ 2.0 - Organizzazione dei sistemi di calcolo

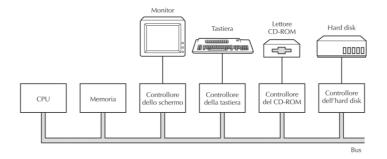

Un calcolatore è un sistema in cui processore, memorie e dispositivi periferici sono connessi tra loro.

**John Von Neumann**, ideatore dell'architettura base dei computer odierni, utilizzava la memoria principale non solo per i dati ma anche per i programmi, evitando così configurazioni complesse con interruttori e cavi. Von Neumann utilizzava l'architettura **bus oriented**, la quale prevedeva un insieme di connessioni elettriche parallele utilizzate per trasportare informazioni da un componente ad un altro.

Questa tipologia di architettura permetteva di utilizzare un numero ridotto di cavi ma causava un grande numero di collisioni.

I sottobus principali sono:

- Sottobus dati, per trasferire dati e programmi tra CPU e memoria centrale

- Sottobus indirizzi, utilizzato dalla CPU per indicare alla memoria le posizioni delle locazioni da trasferire

### ▼ 2.1 - Processore

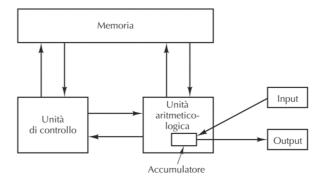

La CPU (Central Processing Unit) è il componente di un elaboratore in grado di leggere ed eseguire le istruzioni dei programmi presenti nella memoria centrale.

# Componenti di una CPU

- Control Unit (CU): legge e interpreta le istruzioni per farle eseguire alla ALU.

- Arithmetic Logic Unit (ALU): esegue le istruzioni decodificate dalla CU (AND, OR, addizione ecc.).

- Registri: memorizzano le informazioni necessarie al funzionamento e i risultati temporanei.

Alcuni registri speciali:

- PC (Program Counter): indica la prossima istruzione in memoria.

- IR (Instruction Register): memorizza l'istruzione che si sta per eseguire.

- MAR (Memory Address Register): indirizzo della prossima cella di memoria da utilizzare nella prossimo lettura/scrittura.

- MDR (Memory Data Register): registro che contiene i dati che devono essere scritti o letti in memoria principale.

- PSW (Program Status Word): contiene informazioni di vario genere sull'ultima operazione eseguita, in questo modo consente una corretta esecuzione del programma in quanto permette al processore di prendere decisioni su come eseguire le istruzioni.

# Esecuzione di una tipica istruzione

Tipicamente la CPU opera tramite un ciclo di esecuzione chiamato **Fetch - Decode - Execute (FDE)**:

- Fetch: Caricamento

- 1. Contenuto di PC posto su MAR e attivazione della linea Leggi.

2. Il contenuto in memoria all'indirizzo indicato da MAR viene scritto su MDR attraverso il bus dati.

#### · Decode: Decodifica

3. Il contenuto di MDR viene copiato in IR e decodificato.

#### • Execute: Esecuzione

- 4. L'istruzione passa in esecuzione nella ALU.

- 5. Se ci sono operandi da prelevare in memoria, si collocano in registri tramite MAR e MDR al fine di velocizzare l'acceso al loro valore.

- 6. Terminata l'esecuzione il risultato va su registro destinazione; se occorre salvarlo in memoria vengono utilizzati MAR e MDR.

- 7. Viene aggiornato il valore di PC e si ritorna al punto 1.

# Ciclo di clock

Il processo che prevede il flusso di dati dai registri alla ALU, l'esecuzione delle operazioni e la riscrittura del risultato nei registri viene chiamato **ciclo di data path**, il quale viene governato dal **ciclo di clock**.

Il ciclo di clock indica l'intervallo temporale tra due clock consecutivi, ovvero tra l'esecuzione di due distinte operazioni. Tramite il clock è possibile scandire la frequenza con la quale vengono eseguite operazioni successive, questo perchè molte volte l'ordine secondo il quale vengono eseguiti gli eventi all'interno di un elaboratore è cruciale, ed è dunque fondamentale fare in modo che non vengano iniziate operazioni prima che quelle precedenti finiscano.

# Microprogrammazione della CPU

Una CPU viene costruita tramite un circuito hardware compatibile con un insieme prefissato di istruzioni. Ciò diventa però complicato nel caso in cui occorre eseguire un set di istruzioni molto amplio, in quanto la costruzione di un hardware compatibile con esso sarebbe troppo complicato e costoso.

Per questo spesso la CPU viene **microprogrammata**, permettendo così un numero più grande di istruzioni utilizzando lo stesso circuito hardware. Inoltre cambiando il microprogramma è possibile modificare il comportamento della CPU (correggendo degli errori, aggiungendo nuove istruzioni ecc.) senza operare sull'hardware.

#### CISC contro RISC

Nella realizzazione di architetture esistono solitamente due filosofie:

### CISC (Complex Instruction Set Computer)

Architetture basate su un **set di istruzioni complesso**, possibile da creare sia lato software (microprogrammazione) che lato hardware.

Questo porta dei vantaggi dal punto di vista dell'esecuzione generale di un programma, in quanto è composto da un numero più piccolo di istruzioni, ma una più lenta velocità di compilazione, in quanto il set di istruzioni è più amplio e quindi anche le diverse casistiche che si possono presentare durante la compilazione sono maggiori, e una più lenta esecuzione di una singola istruzione, in quanto risulta più complicata rispetta a quella di un architettura di tipo RISC.

# RISC (Reduced Instruction Set Computer)

Architetture basate su un **set di istruzioni molto semplice** in grado di aumentare la velocità di esecuzione di ogni singola operazione e la velocità di compilazione.

Tra gli svantaggi troviamo però il fatto che per scrivere uno stesso programma occorre un numero di istruzioni più elevato rispetto a quello di un architettura CISC e quindi una velocità di esecuzione generale del programma più lenta.

Nonostante ciò l'architettura dell'elaboratore è molto più semplice e meno costosa da realizzare.

# Parallelismi, come migliorare le prestazioni di un processore

# Pipelining

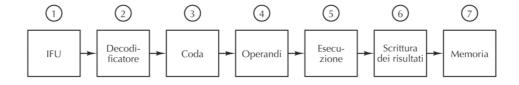

Tramite il pipelining è possibile aumentare le prestazioni di un processore utilizzando diverse sezioni della CPU per effettuare contemporaneamente più cicli FDE (es. mentre un'operazione sta effettuando il decode l'operazione successiva può effettuare il fetch per risparmiare tempo).

Esempio di pipelining con un processore diviso in 5 sezioni differenti. Ogni numero corrisponde a una singola operazione, la quale si può trovare sello stadi S1, S2, S3, S4 oppure S5.

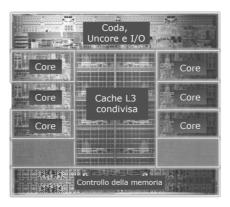

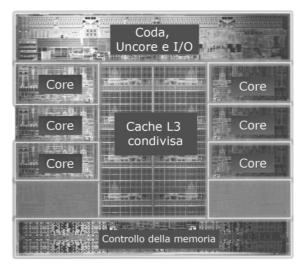

#### Multicore

All'interno della stessa CPU vengono **replicate CU e ALU** al fine di eseguire operazioni in parallelo.

Processore multicore.

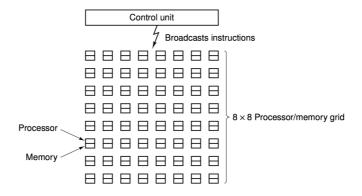

### Array computer

All'interno della stessa CPU vengono **replicate ALU e memorie** al fine di eseguire la stessa operazione in parallelo su dati diversi (Es. modifica di una foto: su ogni pixel deve essere eseguita la stessa operazione). La CU invece viene condivisa.

**SIMD**: Single Instruction-stream, Multiple Data-stream.

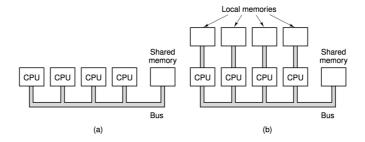

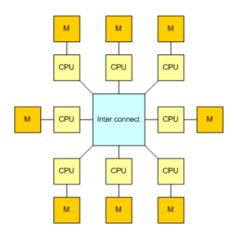

# Multiprocessori

Più CPU condividono la stessa memoria, senza eseguire necessariamente la stessa operazione.

MIMD: Multiple Instruction-stream, Multiple Data-stream.

### Multicomputer

Più CPU che non condividono la stessa memoria e che comunicano tramite dei messaggi; rappresenta la forma più estrema di parallelismo.

# Cosa significa processore basato su 32 o 64 bit?

Questo valore indica quanti bit alla volta vengono letti e scritti dalla CPU nella memoria. Questi blocchi di bit vengono detti word.

#### ▼ 2.2 - Memorie

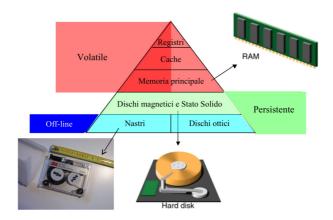

Le **memorie** sono le componenti di un calcolatore che permettono di memorizzare dati e programmi.

Le principali memorie possono essere rappresentate graficamente in una piramide, nella quale andando dal basso verso l'alto si incontrano memorie sempre più veloci e più costose a parità di byte memorizzabili.

Le memorie si possono dividere in base alle loro caratteristiche:

- Volatili: tengono in memoria i dati finchè l'elaboratore viene alimentato.

- Persistenti: l'informazione rimane memorizzata anche quando il calcolatore non è alimentato.

- On-line: i dati sono sempre accessibili.

- Off-line: i dati sono accessibili solo se la memoria è collegata all'elaboratore (ad esempio i dischi ottici devono essere inseriti nell'apposito lettore per essere letti).

# Organizzazione delle memorie

Le memorie si organizzano in **celle**, le quali sono sequenze di bit (in genere 8) con un loro indirizzo.

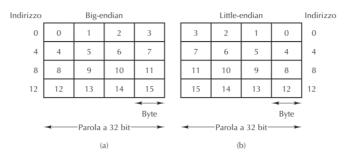

I processori però operano solitamente su blocchi di memoria superiori ad 8 (in genere 32 o 64) e chiamati **word**, e questi vengono organizzati in byte seguendo due modalità: **big endian**, con indirizzi asseganti da sinistra verso destra, e **little endian**, con indirizzi assegnati da destra verso sinistra.

Figura 2.11 (a) Memoria big endian. (b) Memoria little endian.

#### Cache

La **cache** è una memoria molto veloce ma poco capiente. Viene utilizzata per memorizzare le word di memoria utilizzate più di frequente.

Quando la CPU necessita di una word, la cerca prima di tutto nella cache e, se non presente la preleva dalla memoria principale e la inserisce nella cache. Solitamente questo processo di memorizzazione nella cache permette di risparmiare tempo rispetto al semplice prelievo delle word dalla memoria principale, in quanto il tempo medio di accesso viene quantificato con la formula **c+(1-h)m**, dove c è il tempo di accesso alla cache, m il tempo di accesso alla memoria principale e h (valore che va da 0 a 1) la probabilità di trovare l'informazione cercata nella cache. Da questa formula si comprende come più la probabilità di trovare l'informazione nella cache aumenta, più il tempo di accesso equivale a c, mentre con meno probabilità di trovare l'informazione nella cache il tempo equivale a c+m. Ovviamente la probabilità di trovare l'informazione nella cache dipende dalla sua dimensione e da come viene gestito il passaggio dei dati tra cache e memoria centrale.

# Hard Disk e SSD

Un **Hard Disk** è un dispositivo elettro-magnetico che permette di conservare informazioni sotto forma magnetica. Esso è composto da:

- **Testina**: magnetizza porzioni di disco al fine di memorizzare informazioni e legge lo stato di magnetizzazione della superficie del disco.

- Traccia: seguenza circolare di bit.

- **Settore**: porzione di traccia che contiene una quantità prefissata di bit uguale per tutti i settori.

Una **SSD** (**Solid State Drive**) invece è un dispositivo completamente elettronico, il quale non presenta nessuna parte in movimento. Sono più veloci degli hard disk ma più costosi.

# **RAID**

Il RAID (Redundant Array Of Information Disks) è una tecnica di memorizzazione che consiste nell'utilizzare più Hard Disk/SSD al fine di avere una velocità di lettura/scrittura maggiore, in quanto le CPU moderne permettono di effettuare più operazioni in parallelo e dunque sono in grado di leggere da più dischi contemporaneamente, e una migliore affidabilità, in quanto permette di memorizzare informazioni riguardo i dati all'interno di altri dischi in modo che se il disco principale viene danneggiato questo può essere recuperato.

Esistono diverse tipologie di RAID, le quali consistono in diverse tecniche di memorizzazione dei dati:

#### • RAID 0

Consiste nel memorizzare l'informazione suddividendola in più dischi, così che sia la lettura che la scrittura possa essere fatta in parallelo.

#### RAID 1

Consiste nel copiare la stessa informazione su più dischi al fine di aumentare la sicurezza e, se il processore è in grado di leggere la stessa informazione da più dischi diversi anche la velocità viene aumentata.

### • RAID 2-3-4-5

Tecniche che consistono nell'utilizzare in dischi secondari dei byte che permettono di verificare l'integratezza dei dati e di ricostruire l'informazione nel caso essa venga danneggiata.

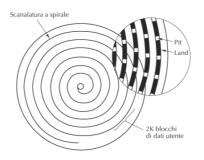

#### Dischi ottici

I dischi ottici sono memorie che utilizzano un principio ottico che consiste nel codificare le informazioni alternando dei fori (Pit) a zone piane (Land). Il disco viene letto tramite un raggio laser che viene riflesso in modo diverso al passaggio di Pit e Land e se individua un passaggio Pit-Land codifica un 1, altrimenti l'assenza di variazioni codifica uno 0.

Le tipologie di dischi ottici sono le seguenti:

- CD-ROM (Read Only Memory): scritto dal costruttore e non riscrivibile.

- CD-R (Read): scrivibile una sola volta.

- CD-RW (Read/Write): riscrivibile più volte.

- DVD (Digital Video Disk).

- Blu Ray: utilizza un laser blu a differenza di quello rosso del DVD, permettendo migliori risoluzioni.

# ▼ 2.3 - Dispositivi di input e output

I dispositivi di input/output più popolari sono i seguenti:

- Tastiera

- Mouse

- Monitor

Richiede una specifica scheda video che contiene un proprio processore chiamato **GPU** (**Graphical Processing Unit**), solitamente basata su architetture multicore avanzate che sono anche programmabili per eseguire programmi non grafici.

### Stampanti

Un dispositivo di input o output si collega al bus tramite un **controller**, il quale contiene la maggior parte dell'elettronica. Alcuni controller accedono direttamente alla memoria senza passare per la CPU, utilizzando una tecnica chiamata **DMA (Direct Memory Access)**. Al termine della scrittura/lettura si invia un segnale interrupt alla CPU per informare il sistema operativo che l'I/O è terminato. Un chip chiamato **arbitro del bus** stabilisce i turni secondo i quali i dispositivi di input/output e la CPU accedono al bus al fine di evitare collisioni.

# ▼ 3.0 - Porte logiche e circuiti combinatori

### ▼ 3.1 - Algebra di Boole

$\ \ L'algebra\ di\ Boole\ definisce\ un'aritmetica\ tra\ i\ due\ valori\ binari\ 0\ e\ 1,\ utilizzati\ dall'elaboratore.$

Gli operatori base di tale algebra sono 3:

- Addizione (A+B oppure **OR**)

- Moltiplicazione ( $A \times B$  oppure **AND**)

- Negazione ( $\overline{A}$  oppure **NOT**)

# Proprietà dell'algebra di Boole

| Name             | AND form                                      | OR form                                       |

|------------------|-----------------------------------------------|-----------------------------------------------|

| Identity law     | 1A = A                                        | 0 + A = A                                     |

| Null law         | 0A = 0                                        | 1 + A = 1                                     |

| Idempotent law   | AA = A                                        | A + A = A                                     |

| Inverse law      | $A\overline{A} = 0$                           | $A + \overline{A} = 1$                        |

| Commutative law  | AB = BA                                       | A + B = B + A                                 |

| Associative law  | (AB)C = A(BC)                                 | (A + B) + C = A + (B + C)                     |

| Distributive law | A + BC = (A + B)(A + C)                       | A(B+C) = AB + AC                              |

| Absorption law   | A(A + B) = A                                  | A + AB = A                                    |

| De Morgan's law  | $\overline{AB} = \overline{A} + \overline{B}$ | $\overline{A + B} = \overline{A}\overline{B}$ |

Nota: le leggi di De Morgan valgono anche su più di 2 variabili.

Nota: le leggi da ricordare sono le 2 leggi distributive e le 2 leggi di De Morgan, in quanto le altre si ricavano da queste.

# ▼ 3.2 - Tabella di verità e formula canonica

# Funzione booleana e tabella di verità

Una **funzione booleana** associa a delle variabili booleane in input un valore booleano in output. Esse possono essere descritte in modo completo tramite una tabella di verità, la quale mostra tutte le combinazioni booleane tra le variabili e i rispettivi output.

| A | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Esempio di tabella di verità-

# Mintermini e espressioni booleane

- Un letterale è una variabile o una variabile negata

- Un **mintermine** su n variabili corrisponde ad un AND logico tra n letterali corrispondenti alle n variabili.

Ogni combinazione dei valori delle variabili di una funzione ha un solo mintermine che fornisce come risultato 1.

| A | В | C | F |                                          |

|---|---|---|---|------------------------------------------|

| 0 | 0 | 0 | 0 | $\overline{A} \overline{B} \overline{C}$ |

| 0 | 0 | 1 | 0 | $\overline{A} \overline{B} C$            |

| 0 | 1 | 0 | 1 | $\overline{A} B \overline{C}$            |

| 0 | 1 | 1 | 0 | $\overline{A}BC$                         |

| 1 | 0 | 0 | 0 | $A \overline{B} \overline{C}$            |

| 1 | 0 | 1 | 0 | $A \overline{B} C$                       |

| 1 | 1 | 0 | 1 | $AB\overline{C}$                         |

| 1 | 1 | 1 | 1 | ABC                                      |

Esempio di mintermini di una funzione che forniscono come risultato 1.

Ogni funzione booleana può essere descritta tramite una funzione creata con il solo utilizzo degli operatori base (AND, OR e NOT). In particolare esiste una funzione detta canonica la quale è molto facile da trovare partendo dalla tabella di verità ma non sempre corrisponde alla forma minima.

Per costruirla occorre trovare i mintermini della funzione nei casi in cui essa assume valore 1 ed effettuare l'operazione OR tra di loro.

$$\overline{A}B\overline{C} + AB\overline{C} + ABC$$

Forma canonica

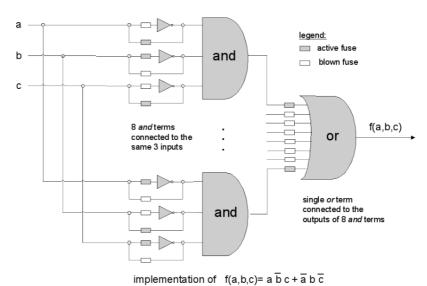

# Array logico programmabili

Siccome tutte le funzioni booleane si possono definire tramite una forma canonica vista in precedenza, è possibile realizzare ogni tipo di circuito avente n input tramite un **array logico programmabile**, il quale prevede porte AND per tutte le possibili combinazioni degli n input, e una porta OR finale tra gli output di tutti i mintermini.

Questo tipo di circuito consente di realizzare tutte le funzioni booleane con n input in quanto presenta dei fusibili lungo i fili che permettono di decidere se interrompere o meno un collegamento e realizzare qualsiasi funzione canonica.

Esempio di array logico programmabile

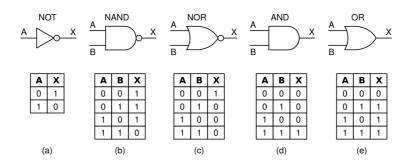

#### ▼ 3.3 - Porte logiche

# **Transistor**

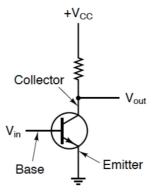

Un **transistor** rappresenta un componente elettronico alla base delle architetture di ogni elaboratore in quanto permette di creare porte logiche. Esso è composto da 3 connessioni: **base** (dove viene dato il valore di input), **collettore** e **emettitore** e funziona in questo modo:

- Se non c'è tensione sulla base, si comporta come una resistenza infinita tra collettore e emettitore.

- Se c'è tensione sulla base, si comporta da conduttore ideale tra collettore e emettitore.

#### **NOT** con transistor

- Se non viene fornita tensione a  $V_{in}$  (input = 0), allora la tensione  $V_{cc}$  (1) viene trasmessa a  $V_{out}$  (output = 1).

- Se viene fornita tensione a  $V_{in}$  (input = 0), allora la tensione  $V_{cc}$  (1) passa dal collettore all'emettitore e viene trasmessa a terra, e non ci sarà tensione su  $V_{out}$  (output = 0).

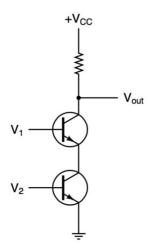

# NAND con transistor

• La tensione va a terra (0) solo se a entrambe le basi ( $V_1$  e  $V_2$ ) viene data tensione, altrimenti  $V_{cc}$  (1) viene trasmessa in output a  $V_{out}$ .

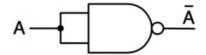

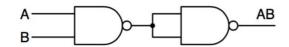

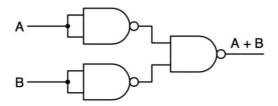

# Porte logiche

È possibile implementare circuiti tramite l'utilizzo di porte logiche.

In particolare utilizzeremo la porta NAND per rappresentare ogni tipo di circuito per 2 principali motivi:

- Facile da realizzare partendo da transistor.

- La porta logica NAND è universale, dunque tramite essa è possibile realizzare qualsiasi altra porta logica partendo da essa.

# NOT

**AND**

OR

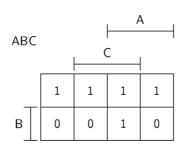

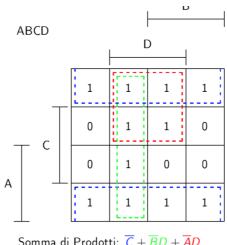

# ▼ 3.4 - Mappa di Karnaugh e formula minimale

# Mappa di Karnaugh

La forma canonica di una funzione è solitamente utile nel caso in cui si voglia utilizzare un PLA, mentre non lo è se si punta all'efficenza di un circuito, in quanto molte volte si riescono ad utilizzare formule con l'ausilio di un numero minore di porte logiche.

Queste funzioni, dette **minimali**, sono realizzabili tramite la creazione preventiva di una tabella bidimensionale simile alla tabella di verità, chiamata **mappa di Karnaugh**. Essa è realizzabile nel seguente modo:

- 1. Creare una tabella bidimensionale il quale numero di righe e colonne è  $2^n$ , con n il numero di letterali presenti nella riga o nella colonna. Quali letterali vanno inseriti nelle righe e nelle colonne della mappa non ha importanza, basta che il successivo riempimento della mappa con gli 0 e gli 1 venga fatto nella maniera corretta rispettando la tabella di verità.

- Scrivere a lato di ogni riga e colonna ogni possibile combinazione dei letterali seguendo il codice gray, il quale permette di realizzare una tabella in cui due celle adiacenti differiscono per un solo letterale.

# Come realizzare il codice gray?

Per ottenere un numero nel codice grey occorre partire dal corrispondente numero binario e fare una XOR bit a bit, ovvero una somma senza riporti, con sè stesso spostato di una cifra a destra.

# Esempio:

6 in decimale → 110 in binario → 101 in gray

110 + (binario)

011(0) = (binario spostato a destra)

101 (gray)

I primi numeri in codice gray sono dunque i seguenti:

| Decimal | Binary code |       |       | Gray code |       |       |       |       |

|---------|-------------|-------|-------|-----------|-------|-------|-------|-------|

| Number  | $B_3$       | $B_2$ | $B_1$ | $B_0$     | $G_3$ | $G_2$ | $G_1$ | $G_0$ |

| 0       | 0           | 0     | 0     | 0         | 0     | 0     | 0     | 0     |

| 1       | 0           | 0     | 0     | 1         | 0     | 0     | 0     | 1     |

| 2       | 0           | 0     | 1     | 0         | 0     | 0     | 1     | 1     |

| 3       | 0           | 0     | 1     | 1         | 0     | 0     | 1     | 0     |

| 4       | 0           | 1     | 0     | 0         | 0     | 1     | 1     | 0     |

| 5       | 0           | 1     | 0     | 1         | 0     | 1     | 1     | 1     |

| 6       | 0           | 1     | 1     | 0         | 0     | 1     | 0     | 1     |

| 7       | 0           | 1     | 1     | 1         | 0     | 1     | 0     | 0     |

| 8       | 1           | 0     | 0     | 0         | 1     | 1     | 0     | 0     |

| 9       | 1           | 0     | 0     | 1         | 1     | 1     | 0     | 1     |

| 10      | 1           | 0     | 1     | 0         | 1     | 1     | 1     | 1     |

| 11      | 1           | 0     | 1     | 1         | 1     | 1     | 1     | 0     |

| 12      | 1           | 1     | 0     | 0         | 1     | 0     | 1     | 0     |

| 13      | 1           | 1     | 0     | 1         | 1     | 0     | 1     | 1     |

| 14      | 1           | 1     | 1     | 0         | 1     | 0     | 0     | 1     |

| 15      | 1           | 1     | 1     | 1         | 1     | 0     | 0     | 0     |

Tabella decimale, binario, gray dei numeri da 0 a 15.

# 3. Riempire la tabella inserendo 0 e 1 a seconda delle combinazioni dei letterali

| Α | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

# Come ricavare la formula minimale dalla mappa di Karnaugh?

All'interno della mappa di Karnaugh appaiono gruppi adiacenti di 1 formati dagli stessi letterali. Per ricavare la formula minimale occorre individuare questi gruppi rispettando alcune regole:

- Tutte le celle dei raggruppamenti contengono 1

- Il numero di celle in un raggruppamento deve essere in potenza di 2 (1, 2, 4 ...)

- I raggruppamenti non devono essere potenzialmente inclusi in raggruppamenti più grandi (altrimenti si otterrebbe una formula corretta ma non minimale)

- I raggruppamenti possono essere fatti anche continuando oltre la fine della mappa (effetto pacman).

A questo punto occorre considerare l'OR tra i mintermini costituiti dai letterali che formano il raggruppamento, come nell'esempio:

Somma di Prodotti:  $\overline{C} + \overline{B}D + \overline{A}D$

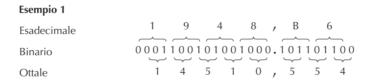

# ▼ 4.0 - Rappresentazione dell'informazione

### ▼ 4.1 - Numeri interi

# Sistemi di numerazione posizionale

Data una codifica in base b, è possibile rappresentare un numero con tale codifica utilizzando cifre da 0 a b-1.

Sia  $d_k d_{k-1} ... d_0$  un numero codificato in base b, per avere lo stesso numero convertito in decimale occorre utilizzare la seguente formula  $\sum_{i=0...k} d_i * b^i$ .

# Codifiche posizionali in informatica

In informatica le codifiche posizionali più utilizzate sono il binario (base 2), l'ottale (base 8) e l'esadecimale (base 16), per via del fatto che la conversione di numeri tra queste codifiche è più semplice che con il decimale.

Ogni cifra in esadecimale corrisponde infatti esattamente a 4 cifre binarie e ogni cifra in ottale corrisponde esattamente a 3 cifre binarie, dunque la conversione avviene nel seguente modo.

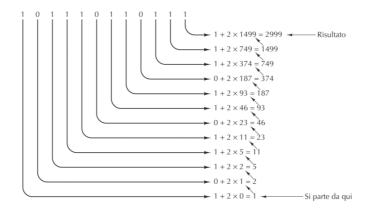

### Conversione binario-decimale

Per convertire un numero da binario a decimale, oltre all'utilizzo della formula generale per la conversione in decimale, è possibile utilizzare la tecnica delle moltiplicazioni successive: partendo dalla cifra più significativa e da un accumulatore uguale a 0, occorre sommare alla cifra del numero in binario il prodotto tra il numero 2 e l'accumulatore, il quale acquisisce il valore del numero più a destra.

Per effettuare la conversione da decimale a binario invece è possibile utilizzata la tecnica inversa, la quale consiste nel dividere ripetutamente per 2 il numero decimale e considerando i resti delle divisioni in ordine inverso di generazione.

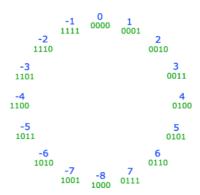

# Codifica di numeri con segno

Per codificare un **numero con segno** si possono utilizzare diverse tecniche:

### Modulo e segno

Si usa il bit più a sinistra per il segno: **0 = positivo**, **1 = negativo**.

Esempio: 00001101 = 13, 10001101 = -13

#### Complemento a 1

Si usa il bit più a sinistra per il segno, ma se il numero è negativo i restanti bit vengono invertiti. A differenza della tecnica con modulo e segno permette di effettuare operazioni aritmetiche in maniera più semplice.

Esempio: 00001101 = 13, 11110010 = -13

# Complemento a 2

Si usa il bit più a sinistra per il segno ma se il numero è negativo i restanti bit vengono invertiti e aggiunto 1. È il metodo più utilizzato in informatica per rappresentare i numeri con segno. L'aggiunta di un 1 per i numeri negativi permette di rappresentare un numero in più con la stessa quantità di bit rispetto al complemento a 1, in quanto in quest'ultima codifica era possibile rappresentare il numero 0 con due codifiche differenti (00000000 e 11111111).

Esempio: 00001101 = 13, 11110011 = -13

Se si considera un numero in complemento a 2 come un numero binario normale, si ottiene un numero positivo che sta in relazione con il corrispondente numero negativo secondo la formula:

$$2^k - m = n$$

- k = numero di bit

- m = valore del numero binario in complemento a 2

- n = modulo del numero negativo

Esempio utilizzando 8 bit:

### Codifica in eccesso

Consiste nel sottrarre  $2^{k-1}$  o  $2^{k-1}-1$  (dipende dalla codifica che viene usata, solitamente si dice codifica in eccesso n per determinare quale numero bisogna sottrarre al valore decimale del numero rappresentato) al numero decimale corrispondente al numero binario per ottenere il numero decimale nella codifica. Questo permette di spostare l'intervallo dei numeri al fine di rappresentare con i numeri negativi con i primi  $2^{k-1}$  numeri.

Esempio: in codifica ad eccesso 128, 00000000 = -128, 10000000 = 0, 11111111 = 127

### Numeri rappresentabili in base alle codifiche

- Numeri naturali non negativi:  $[0, 2^k-1]$

- Modulo e segno o complemento a 1:  $[-2^{k-1}+1, 2^{k-1}-1]$

- Complemento a 2 o codifica in eccesso: [- $2^{k-1}$ ,  $2^{k-1}$ -1]

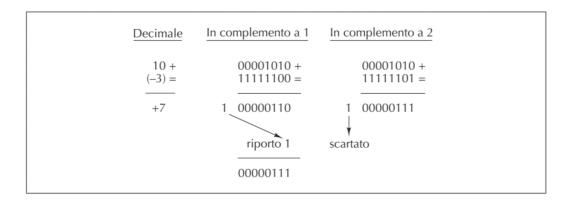

# Somma in complemento a 1 e 2

Le codifiche in complemento a 1 e a 2 vengono utilizzate per la loro efficacia nell'operazione della somma, in quanto in entrambe i casi, sia se i due numeri sono entrambe positivi che se uno dei due è negativo, basta sommare **bit a bit** i due numeri.

Nel complemento a 1 però, se c'è un riporto questo viene sommato al risultato, mentre nel complemento a 2 il riporto viene scartato.

Nell'operazione di somma per i numeri a complemento a 1 e a 2 vi è **overflow** solo nel caso in cui i due addendi sono dello stesso segno e il risultato è di segno opposto.

### ▼ 4.2 - Numeri con la virgola

### Perchè il floating point?

I numeri con la virgola in informatica non vengono rappresentati nella maniera classica, ovvero a virgola fissa, in quanto questa tecnica spesso non è molto efficace a causa del maggiore consumo di **memoria** e per la **difficoltà nei calcoli**.

Per questo motivo viene utilizzata la tecnica del **floating point**, la quale consiste nel rappresentare un numero con la virgola utilizzando due interi distinti, la **mantissa** (o **frazione**) e l'**esponente**.

# Esempio:

Nonostante gli elaboratori lavorino in base 2 facciamo un esempio utilizzando numeri in base 10 al fine di comprendere meglio il concetto.

Mettiamo caso che venga utilizzata la tecnica classica con virgola fissa, e in uno stesso calcolo vengano utilizzati due numeri, uno molto grande come 30000000, e l'altro molto piccolo come 0.00000015.

Innanzitutto capiamo come la loro **memorizzazione** è molto dispendiosa in quanto occorrerebbe una notazione che tenga conto di almeno 9 cifre a sinistra della virgola e 8 cifre a destra della virgola. Inoltre, molte delle **operazioni** che verranno effettuate tra questi 2 numeri risulteranno complicate, come ad esempio la moltiplicazione la quale prevede di moltiplicare tutte le cifre dei due numeri tra loro e poi di sommare i risultati.

Per questi motivi è utile rappresentare questi due numeri tramite un'altra tecnica, quella del floating point, la quale ci consentirebbe di rappresentarli nella seguente maniera:

- $\circ$  300000000 = 3 × 10<sup>8</sup>.

- $\circ 0.00000015 = 1.5 \times 10^{-7}$ .

In questo modo si otterranno dei vantaggi sia in termini di memoria, in quanto per ognuno dei due numeri sarà sufficiente memorizzare la mantissa e l'esponente i quali sono molto più piccoli dei numeri dai quali siamo partiti, che in termini di performance, in quanto ad esempio per l'operazione di moltiplicazione basterà moltiplicare le due mantisse e sommare i due esponenti:

$$300000000 \times 0.00000015 = 3 \times 1.5 \times 10^{8-7} = 4.5 \times 10 = 45.$$

La stessa tecnica può essere utilizzata per rappresentare i numeri in base 2 utilizzando come moltiplicatore  $2^n$ , ad esempio  $0.0101=0.101\times 2^{-1}$ .

### Conversione da decimale a binario di numeri con la virgola

Prima di rappresentare un numero decimale in notazione floating point al fine di memorizzarlo all'interno di un computer occorre prima **convertirlo in binario**.

Per fare ciò occorre dividere il numero nella parte intera e quella decimale ed effettuare la conversione in maniera separata:

- Per la parte intera la conversione avviene nella maniera classica, ovvero con le successive divisioni per 2 del numero con la considerazione del resto di ogni divisione.

- Per la parte decimale la conversione avviene moltiplicando per 2 consecutivamente il numero e togliendo la parte intera del numero ad ogni moltiplicazione fino ad arrivare al numero 0.

# Esempio:

$\circ$  Convertire il numero  $28.125_{10}$  in binario.

Parte intera.

$$28|0$$

$14|0$

$7|1$

$3|1$

$1|1$

$0$

$28_{10} = 11100_2$

Parte decimale.

$$\begin{array}{c} 0.125*2=0.250|0\\ 0.250*2=0.5|0\\ 0.5*2=1.0|1\\ 0\\ 0.125_{10}=0.001\\ 28.125_{10}=11100.001_2 \end{array}$$

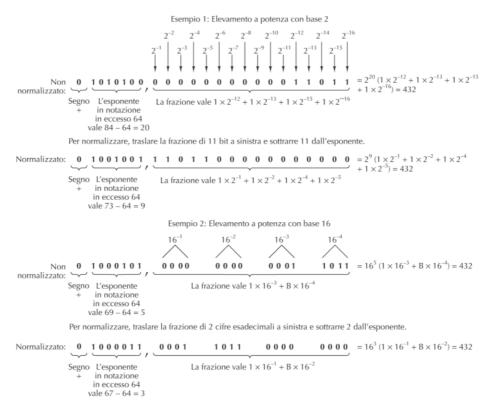

# Notazioni floating point

Siccome tramite la codifica floating point è possibile rappresentare uno stesso numero in molti modi diversi (es.  $30_{10}=((3\times 10^1)_{10}=(300\times 10^{-1})_{10}=(1111\times 2^1)_2)$  esistono diversi standard che definiscono le regole nella rappresentazione dei numeri.

In genere tutti gli standard che gli elaboratori utilizzano seguono queste regole principali:

- La mantissa e l'esponente vengono rappresentati come interi in base 2, 4, 8 o 16.

- Viene utilizzata una mantissa minore di 1.

- La mantissa viene solitamente **normalizzata**, ovvero per ottimizzare la memoria utilizzata la cifra più significativa di questa non è mai uguale a 0.

Rappresentazioni floating point del numero 432 in base 2 non normalizzata, base 2 normalizzata, base 16 non normalizzata e base 16 normalizzata.

# Standard IEEE 754

Lo standard IEEE 754 è il più usato per rappresentare numeri floating point.

Esso definisce diversi formati tra i quali single (BINARY32) e double (BINARY64) precision. Il **BINARY32** presenta le seguenti caratteristiche:

- 1 bit per il segno del numero.

- 8 bit di esponente, il segno viene espresso tramite la notazione in eccesso 127 (bisogna sottrarre 127 al corrispondente numero decimale per conoscere il valore dell'esponente).

- 23 bit di mantissa. La rappresentazione della mantissa è particolare rispetto agli altri standard in quanto siccome qualunque numero normalizzato ha come prima cifra della mantissa 1 allora questa non ha necessità di essere memorizzata, e dunque quella cifra la si lascia prima della virgola.

### Esempio:

- Convertire il numero -30.375 in binario utilizzando lo standard floating point IEEE 754.

- 1. Convertire il numero 30.375 in binario:

- Parte intera:  $30_{(10)} = 11110_{(2)}$ .

- Parte decimale:  $0.375_{(10)} = 0.011_{(2)}$ .

Quindi,

$$30.375_{10} = 11110.011_2$$

2. Normalizzare il numero binario ottenuto lasciando un 1 prima della virgola:

$$11110.011 = 1.1110011 \times 2_{(2)}^4$$

3. Convertire l'esponente in binario utilizzando la notazione in eccesso 127:

$$127 + 4 = 131_{(10)} = 10000011_{(2)}$$

.

4. Inserire l'esponente e la mantissa nelle giuste postazioni ricordando che il bit di segno deve essere 1 per via del fatto che il numero è negativo:

### Problemi nella rappresentazione floating point

Nonostante ci si aspetti che i calcoli di un computer siano estremamente accurati è possibile incorrere in **errori nei risultati** di alcuni calcoli con i numeri con la virgola.

Questo perchè a differenza di noi umani un computer utilizza solo numeri in base 2, i quali possono presentare la **periodicità** anche quando il corrispondente numero in decimale non la presenta. Ad esempio il numero 0.2 in decimale equivale a  $0.0\overline{0011}$  in binario. Il problema dunque risiede nel fatto che il computer non può memorizzare e lavorare con una quantità di cifre infinite, dunque ha necessità di troncare un numero periodico, e così facendo possono essere riscontrati problemi in alcune operazioni che utilizzano questi tipi di numeri (Es. alcuni compilatori possono fornire come risultato dell'operazione 0.1+0.2 il numero  $0.300000\ldots 1$ ).

#### ▼ 4.3 - Caratteri

Per rappresentare i caratteri utilizzando dei bit esistono diverse **codifiche** che differiscono per il numero di bit utilizzati e dal loro significato.

#### **ASCII**

La codifica **ASCII (American Standard Code for Information Interchange)** è una codifica largamente diffusa che utilizza **7 bit** per rappresentare i principali simboli alfanumerici anglosassoni e per alcuni caratteri speciali.

#### UNICODE

Siccome la codifica ASCII prende in considerazione solamente i caratteri dell'alfabeto anglosassone, esistono altre codifiche, come la UNICODE, che utilizzano una quantità maggiore di bit al fine di tenere conto anche di altri alfabeti.

La UNICODE utilizza infatti 16 bit con i quali è possibile rappresentare i caratteri di diversi alfabeti, i quali caratteri vengono messi in intervalli contigui di codici, ed è anche compatibile con la codifica ASCII in quanto se i primi 9 bit vengono messi a 0 con i restanti 7 bit è possibile rappresentare i caratteri dell'alfabeto anglosassone. Inoltre esistono codici all'interno dell'UNICODE che non sono stati ancora assegnati al fine di poter rappresentare in futuro nuovi caratteri.

# UTF-8

**UTF-8 (Unicode Transformation Format)** è una codifica più ottimizzata rispetto all'UNICODE in quanto può dinamicamente utilizzare **da 1 a 4 byte** a seconda dell'informazione da codificare. I bit iniziali infatti indicano la quantità di bit utilizzati (es. se il bit iniziale è 0, i restanti 7 bit contengono una codifica ASCII).

### ▼ 4.4 - Codici correttori

Occasionalmente le memorie di un elaboratore possono commettere degli errori in fase di scrittura, lettura o in fase di trasmissione, spesso a causa di picchi di tensione sulle linee di alimentazione. Per proteggersi da questi errori, le memorie utilizzano dei codici di rilevazione e/o

correzione degli errori, i quali consistono nell'aggiunta di bit extra alla parola da memorizzare che verranno controllati nel momento in cui il dato verrà letto.

### Distanza di Hamming di due sequenze

La **distanza di Hamming** indica il numero di bit per i quali due sequenze di bit differiscono tra loro, ad esempio i due byte 10010111 e 10010001 hanno una distanza di Hamming di 2 bit.

#### Parola di codice

Come abbiamo detto in precedenza, per rilevare e/o correggere gli errori in una sequenza di codice occorre aggiungere dei bit di controllo a tale sequenza. Supponiamo dunque di avere una parola di memoria che consiste in m bit di dati ai quali vengono aggiunti r bit di controllo; si otterrà dunque una sequenza lunga n = m + r, la quale viene chiamata **parola di codice**. I bit di controllo aggiuntivi indicano delle proprietà particolari dei bit presenti nella sequenza (es. quantità di bit che hanno valore 1, se i bit che hanno valore 1 sono di quantità pari o dispari ecc.) che permettono, al momento della lettura del dato, di stabilire con più o meno precisione se si sono verificati errori.

#### Distanza di Hamming dell'intero codice

I bit di controllo consentono dunque di ottenere un insieme di parole di codice lecite e altre illecite, nelle quali si sono sicuramente verificati degli errori. Conoscendo la modalità che è stata scelta per inserire i bit di controllo all'interno di una sequenza di codice è possibile costruire una lista completa di tutte le parole di codice lecite. Dopo aver ottenuto questa lista occorre trovare le due parole di codice per le quali la distanza di Hamming è minima, e quella sarà la **distanza di Hamming dell'intero codice**.

#### Quanto deve essere la distanza di Hamming dell'intero codice?

La precisione nel trovare gli errori all'interno di una parola di codice dipende dunque dalla distanza di Hamming dell'intero codice:

- Per rilevare d errori singoli all'interno di una sequenza è necessario un codice con una distanza di Hamming di almeno d + 1.

- **Perchè?** Se con un certo tipo di bit di controllo otteniamo una lista di parole lecite che hanno distanza di Hamming minima corrispondente a d+1, possiamo prendere una qualunque delle parole lecite all'interno della lista e scambiare d bit e otterremo sempre una parola illecita, proprio perchè per raggiungere un'altra parola lecite bisogna scambiare almeno d+1 bit per via della minima distanza di Hamming.

- Per **correggere d errori singoli** all'interno di una sequenza è necessario un codice con una distanza di Hamming di almeno **2d + 1**.

- **Perchè?** Se con un certo tipo di bit di controllo otteniamo una lista di parole lecite che hanno una distanza di Hamming minima corrispondente a 2d + 1, possiamo prendere una qualunque delle parole lecite all'interno della lista e scambiare d bit e otterremo sempre una parola illecita con una distanza di Hamming minore della metà della distanza di Hamming minime, il che significa che sarà più simile alla parola giusta che ad ogni altra parola sbagliata, permettendone così la correzione.

# Esempio:

Questo codice ha una distanza di Hamming equivalente a 5, il che significa che può rilevare al massimo 4 errori e che può correggere 2 errori. Infatti, se arriva la parola di codice 0000000111 il ricevente sa che l'originale doveva essere 0000011111, mentre se un errore triplo modifica per esempio la parola 000000000 nella parola 0000000111 non possono essere effettuate correzioni.

#### Bit di parità

Molti algoritmi di rilevazione e correzione di errori utilizzano **bit di parità**, ossia bit aggiuntivi i quali vengono messi a 0 se la somma dei valori dei bit che controllano è pari, altrimenti a 1. Vengono dunque chiamati bit di parità in quanto la somma del loro valore e dei valori dei bit che controllano è sempre pari.

### Algoritmo di Hamming

L'algoritmo di Hamming stabilisce un metodo per inserire il minor numero di bit di controllo all'interno di una sequenza di codice in modo da correggere tutti gli errori singoli.

Ciascuna delle  $2^m$  parole di memoria legali deve dunque avere n parole di codice illegali a distanza 1 da essa, ognuna corrispondente alla stessa sequenza con 1 bit modificato, ovvero quello in cui può avvenire l'errore. Dunque, siccome ognuna delle  $2^m$  parole di memoria lecita richiede n+1 sequenze di codice a essa dedicate (n per I sequenze che con gli errori e 1 per la sequenza lecita), e visto che il maggior numero di sequenze di codice differenti realizzabile con n bit è  $2^n$ , occorre rispettare la seguente relazione  $(n+1)2^m \le 2^n$ , ovvero  $(m+r+1) \le 2^r$ , nella creazione dell'algoritmo di Hamming (la disequazione stabilisce il minor numero di bit di controllo necessari per correggere errori singoli).

Per facilitare la spiegazione numeriamo la sequenza di codice di lunghezza m+r costruita aggiungendo gli r bit di controllo alla sequenza di partenza in questo modo: si incomincia a numerare partendo da sinistra (la cifra più significativa) e iniziando da 1. Tutti i bit la cui posizione è una potenza di 2 (1, 2, 4, 8, 16...) vengono utilizzati per inserire i bit di controllo che sono bit di parità, mentre i restanti bit vengono utilizzati per i dati. Ciascun bit è controllato dai bit di controllo  $b_1, b_2, \ldots, b_n$  tali che la somma delle loro posizioni è equivalente alla posizione del bit. Ad esempio il bit 5 viene controllato dai bit di controllo 1 e 4 in quanto la loro somma fa 5. Dunque:

- Il bit 1 controlla i bit 1, 3, 5, 7, 9, 11, 13, 15, 17, 19, 21 ecc.

- il bit 2 controlla i bit 2, 3, 6, 7, 10, 11, 14, 15, 18, 19 ecc.

- il bit 4 controlla i bit 4, 5, 6, 7, 12, 13, 14, 15, 20, 21 ecc.

- il bit 8 controlla i bit 8, 9, 10, 11, 12, 13, 14, 15 ecc.

In questo modo per controllare se ci sono dei bit errati basta controllare tutti i bit di controllo: se sono tutti corretti non ci sono stati errori, altrimenti la somma delle posizioni dei bit di controllo errati corrisponde alla posizione del bit errato (nella pratica la posizione ottenuta corrisponde al numero in binario ottenuto mettendo a 1 i bit nelle posizioni dei bit errati).

### Esempi:

• Trovare la parola di codice corrispondente alla parola 1111000010101110 utilizzando l'algoritmo di Hamming.

La parola di codice che troveremo sarà della forma: XX1X111X000010X01110 (al posto delle X vanno inseriti i bit di controllo).

- $\circ~$  Bit di controllo 1: X + 1 + 1 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 0 + 1 + 1 + 1 + 0 + 1 + 1 + 1 + 0 + 1 + 1 + 1 + 0 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 + 1 1 + 1 1 + 1 1 + 1 1 + 1 1 + 1 1 + 1 1 + 1 1 + 1 1

- $\circ$  Bit di controllo 4:  $X+1+1+1+0+1+0+1+1+0=X+6 \Rightarrow X=0$

- $\circ~$  Bit di controllo 8:  $X+0+0+0+0+1+0+1=X+2 \Rightarrow X=0$

- $\circ$  Bit di controllo 16:  $X + 0 + 1 + 1 + 1 + 0 = X + 3 \Rightarrow X = 1$

Sostituendo dunque i valori trovati ai bit di controllo corrispondenti troviamo la seguente parola di codice: 00101110000010101110.

• Correggere la parola di codice 001001100000101101110 costruita tramite l'algoritmo di Hamming.

Occorre controllare se ci sono bit di controllo errati e nel caso sapere quali:

- Bit di controllo 1:  $0 + 1 + 0 + 1 + 0 + 1 + 1 + 0 + 1 + 0 = 5 \Rightarrow$  Non corretto.

- $\circ$  Bit di controllo 2:  $0+1+1+1+0+0+0+1+1+1=6 \Rightarrow$  Corretto.

- $\circ$  Bit di controllo 4:  $0+0+1+1+0+1+0+1+1+0=5 \Rightarrow$  Non corretto.

- Bit di controllo 8:  $0+0+0+0+0+1+0+1=2 \Rightarrow$  Corretto.

- $\circ$  Bit di controllo 16:  $1+0+1+1+1+0=4\Rightarrow$  Corretto.

I bit non corretti sono dunque l'1 e il 4, in quanto la somma dei valori dei bit da loro controllati è dispari. A questo punto è possibile calcolare la posizione del bit errato sommando la posizione dei bit di controllo errati: 1+4=5.

La parola di codice corretta è dunque: 001011100000101101110 .

# ▼ 5.0 - Circuiti sequenziali

Un circuito sequenziale è un circuito i cui valori di output non dipendono solo dai valori attualmente in input, come per i circuiti combinatori, ma anche da quelli degli input precedenti. È dunque tramite questa proprietà dai circuiti sequenziali che è possibile realizzare delle memorie.

# ▼ 5.1 - Latch

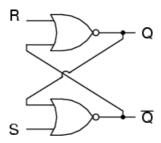

### Latch SR

Il **latch SR** è uno dei circuiti sequenziali più utilizzati. Esso permette di creare una memoria a 1 bit, ed è realizzato nel seguente modo:

Si nota immediatamente come ciascun output generato dai due circuiti NOR vengono riutilizzati come input nell'altra porta NOR del circuito. Analizziamo dunque le **4 combinazioni** dei due input S e R, tenendo in mente la tabella di verità della porta NOR:

### • S = 0, R = 1

La porta NOR con input R restituisce come output Q=0, visto che uno dei due valori in input è 1. Questo output viene poi riutilizzato come input nell'altra porta NOR, quella con input S, restituendo dunque come output  $\overline{Q}=1$ , visto che i due input valgono 0.

Tenendo conto dell'output Q, osserviamo che questo viene messo a 0 se l'input proveniente da R è 1, dunque chiamiamo questo caso il caso di **reset**.

### • S = 1, R = 0

La porta NOR con input S restituisce come output  $\overline{Q}=0$ , visto che uno dei due input ha valore 1. Questo output viene poi riutilizzato come input dell'altra porta NOR, quella con input R, restituendo dunque come output Q=1, visto che i due input hanno valore 0.

Tenendo conto dell'output Q, osserviamo che questo viene messo a 1 se l'input proveniente da S è 1, dunque chiamiamo questo caso il caso di **set**.

### • S = 0, R = 0

Questo caso è diverso dai due precedenti, ed è la causa per la quale questo è un circuito sequenziale. Se ragioniamo infatti come abbiamo fatto per i due casi precedenti notiamo come i due valori in output non si possono conoscere sapendo soltanto i due valori in input, in quanto gli output delle due porte NOR non dipendono dai due input S e R, entrambi aventi valore 0.

Bisogna in questo caso prendere in considerazione lo stato precedente del circuito, ovvero considerare i due valori in output Q e  $\overline{Q}$ . Visto che uno è il contrario dell'altro si formano due casi:

### $\circ$ Q = 0

Il valore di Q = 0 viene utilizzato come input della porta NOR con input S, restituendo come output il valore  $\overline{Q}=1$ . D'altra parte, il valore in output proveniente dall'altra porta NOR con input R sarà ancora Q=0, in quanto uno dei due valori in input è 1.

Notiamo dunque che i due valori in output rimangono gli stessi dello stato precedente e non vengono modificati.

### • Q = 1

Il valore di Q = 1 viene utilizzato come input della porta NOR con input S, restituendo come output il valore  $\overline{Q}=0$ . D'altra parte, il valore in output proveniente dall'altra porta NOR con input R sarà ancora Q=1, in quanto entrambi gli input hanno valore 0.

Anche in questo caso dunque i due valori in output rimangono i medesimi dello stato precedente e non vengono modificati.

In conclusione possiamo notare che in questo caso i valori in output non dipendono da quelli in input, ma dagli output dello stato precedente del circuito, i quali in tutti i casi non vengono modificati. Chiamiamo quindi questo caso lo **stato di memorizzazione**.

### • S = 1, R = 1

Quest'ultimo caso invece non viene preso in considerazione in quanto forma delle **contraddizioni**:

• Considerando che S = 1 equivale a fornire il comando set al circuito e che R = 1 equivale al comando reset, non ha senso utilizzare questi due comandi contemporaneamente, in

quanto ognuno di essi dovrebbe fornire un valore differente per l'output Q.

• Inoltre, nel caso in cui si passi dallo stato avente input S = 1, R = 1 allo stato S = 0, R = 0, non si saprebbe che valori inviare in output, in quanto siccome nel primo stato il circuito fornisce in output due 0, quando si passa al secondo stato le due porte hanno entrambe input 0 - 0, il che dovrebbe dare in output il valore 1 che dovrebbe poi essere passato in input all'altra porta causando un output di 0. I valori in output dunque dipendono da quale delle due porte fornisce per prima il valore in output, portando ad una situazione non ben definita.

Questi due valori in input non vengono dunque mai forniti a questo tipo di circuito.

In seguito a questo considerazioni possiamo formare la tabella di verità:

| S | R | $Q_t$     | $\overline{Q}_t$     | State     |

|---|---|-----------|----------------------|-----------|

| 0 | 0 | $Q_{t-1}$ | $\overline{Q}_{t-1}$ | memory    |

| 0 | 1 | 0         | 1                    | reset     |

| 1 | 0 | 1         | 0                    | set       |

| 1 | 1 |           |                      | undefined |

A questo punto può sorgere una domanda: non è possibile creare una memoria utilizzando una semplice porta logica il quale output viene connesso al suo stesso input al fine di memorizzare un certo dato? Sì, è possibile, ma in questo caso occorrerebbe continuare ad alimentare il circuito al fine di mantenere il dato in memoria, mentre tramite l'utilizzo di un Latch SR è possibile continuare a memorizzare il dato anche dopo aver scollegato il circuito dall'alimentazione, anche se durante questo periodo non sarà possibile modificare il dato in memoria.

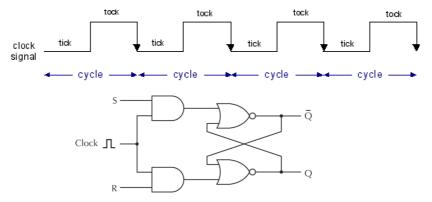

# Latch SR temporizzato

Spesso è preferibile impedire che il Latch cambi di stato se non in specifici momenti, in quanto per esempio alcune operazioni di addizione ad n bit possono non essere terminate e, se non ne viene impedita la memorizzazione vengono passati in memoria dati non esatti.

Per questo motivo il circuito viene ampliato con l'utilizzo di un **clock**, ovvero un segnale 0/1 che, implementato con delle porte AND al latch consente di bloccare o far passare i due valori S e R in input. Nel caso in cui i due valori vengono bloccati infatti si fornirebbe in input al circuito due valori 0 - 0, tenendolo in stato di memoria.

Questo comportamento è detto **commutazione a livello**, ovvero che il livello 1 del clock permette il cambio di stato.

Grafico del segnale di Clock e implementazione del clock nel Latch SR.

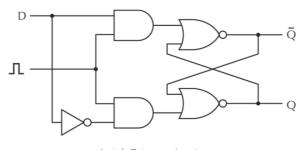

# **Latch D temporizzato**

Per essere sicuri che la situazione **S = 1**, **R = 1** non si verifichi mai viene solitamente utilizzato il circuito **latch D temporizzato**, il quale ha un solo input che viene passato ad S e negato per R. In questo modo i due input S e R sono sempre uno la negazione dell'altro, mentre per la situazione 0 - 0 vengono utilizzati i due AND del clock, i quali bloccano l'input.

Latch D temporizzato

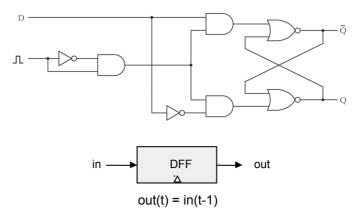

# ▼ 5.2 - Flip-Flop

# **Data Flip-Flop**

In molti circuiti è necessario memorizzare il valore di un particolare istante di tempo, dunque il tempo in cui il clock permette di rilevare nuove informazioni è molto minore rispetto a quello in cui il circuito memorizza l'informazione.

Per fare ciò si utilizzano circuiti con **commutazione sul fronte**, nei quali il cambio di stato avviene negli istanti in cui il segnale proveniente dal clock è in discesa  $(1 \rightarrow 0)$  o in salita  $(0 \rightarrow 1)$ . A differenza del Flip-Flop i Latch temporizzati utilizzavano una **commutazione a livello**, la quale permette un cambio di stato nel momento in cui il segnale proveniente dal clock è 1.

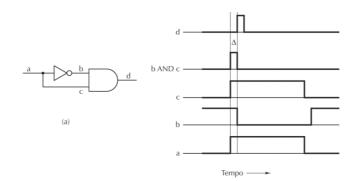

Per fare in modo che il clock restituisca valore 1 solo in fase di salita si utilizza il seguente circuito, avente in input il segnale di clock:

In questo modo, siccome un segnale che passa attraverso una porta logica impiega più tempo a propagarsi nel circuito, vi sarà un istante specifico, quando il segnale di clock cambia dal valore 0 al valore 1, in cui la porta AND finale restituisce valore 1, in quanto i due segnali in ingresso sono entrambi 1 per via del fatto che il segnale non è ancora stato negato nella porta NOT.

Notiamo infatti dal grafico a destra questo fenomeno: **a** rappresenta il segnale di clock, **b** rappresenta il segnale di clock negato, il quale ha uno sfasamento per via del passaggio nella porta NOT, **c** rappresenta il segnale nel circuito che va in input alla porta AND, il quale anche lui ha un piccolo sfasamento rispetto al segnale di clock, ma è irrilevante rispetto allo sfasamento

creato dalla porta NOT. Il segnale di output **d** infine rappresenta lo stesso dell'AND tra b e c sfasato del ritardo con cui la porta AND propaga il segnale nel circuito, dunque notiamo come l'impulso generato dalla variazione del segnale di clock arrivi al latch un pò in ritardo. Occorre inoltre sottolineare il fatto che il vantaggio dell'architettura flip-flop è di essere di facile comprensione, ma nella realtà vengono spesso utilizzate architetture più complesse.

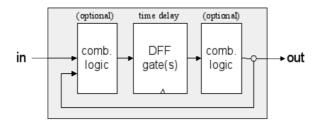

Esistono diversi tipi di flip-flop, noi considereremo il flip-flop di tipo D, il quale viene implementato nel seguente modo:

Il triangolo in basso indica che si tratta di un circuito temporizzato.

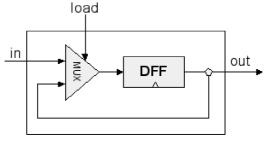

# ▼ 5.3 - Registri e memorie

# 1 bit register

Abbiamo visto come il DFF permette di mantenere l'input dato nella fase di salita del clock fino alla prossima salita. Il problema a questo punto, nel caso in cui si voglia creare una memoria, consiste nel fatto che alla prossima salita del clock il DFF restituirà in output i nuovi valori dati in input, dunque ad ogni clock il valore memorizzato cambierà.

Per ovviare a questo problema e costruire dunque una **memoria a 1 bit** occorre utilizzare il DFF assieme ad un circuito combinatorio costituito da un multiplexer, il quale a seconda del valore del selettore decide se continuare a memorizzare il vecchio output oppure iniziare a memorizzare un nuovo input.

1 bit register.

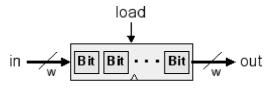

# Multi-bit register

Il **multi-bit register** consente di creare una memoria con un singolo blocco di w bit al suo interno. L'idea è di utilizzare un 1 bit register per ognuno degli w bit del bus in input e collegare ognuno degli 1 bit register al medesimo load.

Multi-bit register.

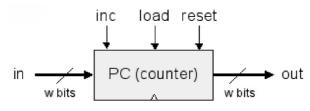

# Counter

Il **counter** è un altro circuito sequenziale largamente usato per realizzare il **Program Counter (PC)** che indica la locazione di memoria da cui prelevare la prossima istruzione da eseguire.

Funziona come un registro con l'unica differenza che presenta due ulteriori bit di input: **inc** e **reset.** Il primo, se attivo, comanda al counter di incrementare di 1 bit il suo valore, al fine di passare alla prossima istruzione, mentre il secondo, se attivo, azzera il counter.

Program Counter (PC).

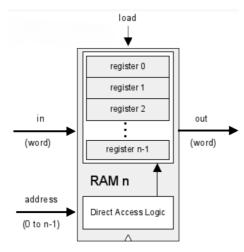

#### Memoria

Una **memoria** con n locazioni da w bit può essere realizzata da n multi-bit register controllati da un Direct Access Logic, ovvero un circuito che gestisce la memoria indicando quale dei registri al suo interno deve essere letto o scritto nel caso in cui load è attivo.

Memoria con n locazioni.

Solitamente torna utile inserire un ulteriore circuito combinatorio dopo le uscite dei singoli registri al fine di decidere quale di questi portare in output.

In generale, come abbiamo visto, un circuito sequenziale può possedere o meno circuiti combinatori prima o dopo i flip-flop.

Struttura generica di un circuito seguenziale.

### ▼ 6.0 - Microarchitettura

Il **livello di microarchitettura** fa da ponte per i livelli logico digitale e ISA, in quanto utilizza i componenti del primo livello per realizzare le componenti utilizzabili fornendo in input alla macchina istruzioni ISA, definendo anche come queste devono essere composte per far funzionare la macchina in modo corretto.

Nonostante oggi esistano microarchitetture molto sofisticate noi inizieremo con l'analizzarne una molto semplice, ovvero quella del **processore Hack**, per poi passare ad introdurre aspetti tipici degli elaboratori più complessi, come la **cache**, il **pre-fetch** delle istruzioni e la **pipeline**.

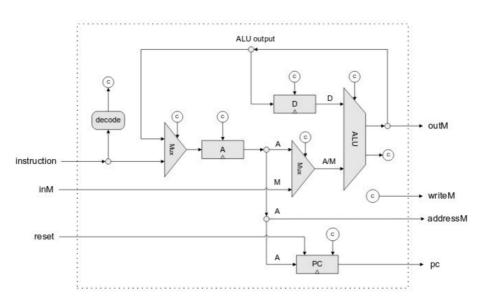

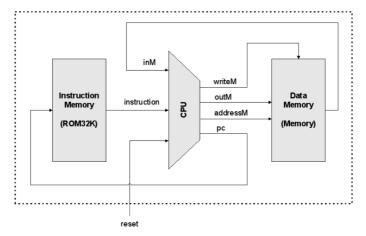

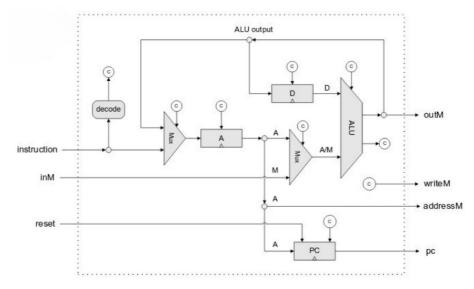

# ▼ 6.1 - Microarchitettura del processore Hack

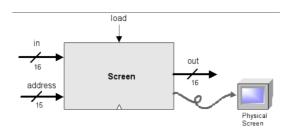

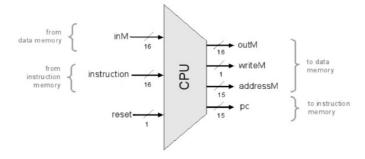

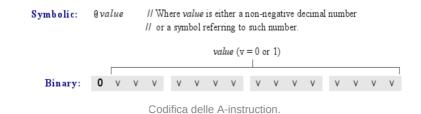

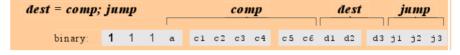

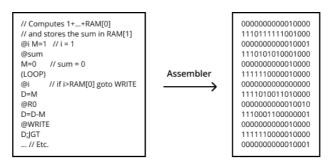

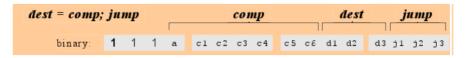

Microarchitettura del processore Hack.

Come è possibile vedere dalla figura il processore del computer Hack prende in input un'istruzione derivante dalla ROM ed utilizza i suoi bit come bit di controllo (i simboli c in figura rappresentano dei bit dell'istruzione). Il processore è composto dalla ALU, 3 registri (A, D e PC) e altre componenti di base che ne consentono il giusto funzionamento.

Seguendo la figura abbiamo che:

- Nel registro A può essere memorizzato un dato contenuto nell'istruzione oppure l'output della ALU.

- Nel registro D può essere memorizzato solo l'output proveniente dalla ALU.

- Nel **registro PC** può essere memorizzato il contenuto del registro A oppure l'input reset gli può comandare di essere rispristinato a 0.

• La **ALU** prende come primo input il contenuto del registro D e come secondo input uno tra il contenuto del registro A e un dato proveniente dalla memoria.

L'intero **ciclo Fetch-Decode-Execute** del processore Hack viene eseguito completamente durante un **singolo ciclo di clock**, dunque un'istruzione in ingresso al tempo t viene completamente eseguita prima del tempo t + 1, nel quale verrà eseguita l'operazione successiva.

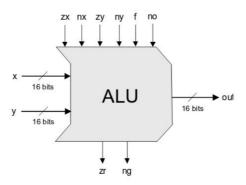

# **ALU**

ALU del computer Hack.

La **ALU** (Arithmetic and Logic Unit) del computer Hack è un componente interno della CPU che esegue operazioni su due parole in input da **16 bit** e restituisce un risultato in output a **16 bit**.

L'operazione da svolgere di volta in volta viene identificata dai **bit di controllo**, ovvero 6 bit in input ognuno dei quali indica una diversa operazione da fare:

| These bit | ts instruct   | These bit | s instruct | This bit selects | This bit inst. | Resulting |

|-----------|---------------|-----------|------------|------------------|----------------|-----------|

| how to    | how to preset |           | preset     | between          | how to         | ALU       |

| the x     | input         |           | input      | + / And          | postset out    | output    |

| zx        | nx            | zy        | ny         | f                | no             | out=      |

|           |               |           |            | if f then        |                |           |

| if zx     | if nx         | if zy     | if ny      | out=x+y          | if no          |           |

| then      | then          | then      | then       | else             | then           |           |

| x=0       | x=!x          | y=0       | y=!y       | out=x&y          | out=!out       | f(x,y)=   |

| 1         | 0             | 1         | 0          | 1                | 0              | 0         |

| 1         | 1             | 1         | 1          | 1                | 1              | 1         |

| 1         | 1             | 1         | 0          | 1                | 0              | -1        |

| 0         | 0             | 1         | 1          | 0                | 0              | x         |

| 1         | 1             | 0         | 0          | 0                | 0              | У         |

| 0         | 0             | 1         | 1          | 0                | 1              | !x        |

| 1         | 1             | 0         | 0          | 0                | 1              | !y        |

| 0         | 0             | 1         | 1          | 1                | 1              | -x        |

| 1         | 1             | 0         | 0          | 1                | 1              | -у        |

| 0         | 1             | 1         | 1          | 1                | 1              | x+1       |

| 1         | 1             | 0         | 1          | 1                | 1              | y+1       |

| 0         | 0             | 1         | 1          | 1                | 0              | x-1       |

| 1         | 1             | 0         | 0          | 1                | 0              | y-1       |

| 0         | 0             | 0         | 0          | 1                | 0              | x+y       |

| 0         | 1             | 0         | 0          | 1                | 1              | x-y       |

| 0         | 0             | 0         | 1          | 1                | 1              | y-x       |

| 0         | 0             | 0         | 0          | 0                | 0              | x&y       |

| 0         | 1             | 0         | 1          | 0                | 1              | x   y     |

Uso dei control bit per identificare l'operazione da svolgere.

Oltre al risultato a 16 bit, la ALU del computer Hack presenta altri due bit di output, **zr** e **ng**, i quali vengono messi a 1 rispettivamente se il risultato è uguale a 0 o se il risultato è negativo. Questo

serve per agevolare le operazioni di salto, le quali controllano se il risultato è 0, se è positivo/negativo, o una combinazione delle due cose.

Come notiamo tra le operazioni che la ALU è in grado di effettuare troviamo operazioni di complemento bit a bit, realizzabili tramite porte not, and bit a bit e or bit a bit. Le uniche operazioni che non siamo in grado di effettuare in questo momento tramite delle porte logiche sono le operazioni di somma e sottrazione, le quali possono però essere implementate tramite l'utilizzo di un adder.

#### Adder

Adder del computer Hack.

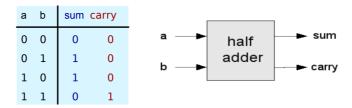

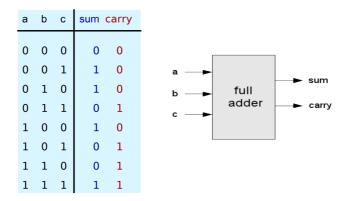

L'adder del computer Hack è un circuito progettato per sommare due interi a 16 bit. Esso viene implementato utilizzando un half adder e 15 full adder.

L'half adder, il quale svolge la somma tra 2 bit, viene implementato a sua volta utilizzando una porta xor per il **risultato della somma** e una porta and per il **riporto**.

Half adder del computer Hack.

Il **full adder** invece svolge la somma tra 3 bit e viene implementato utilizzando 2 Half Adder che svolgono la somma tra i 3 bit e una porta or che controlla se in una delle due operazioni di somma c'è stato almeno un riporto.

Full Adder del computer Hack.

Il risultato dell'unione di half adder e full adder nell'adder del computer Hack è quello di una classica somma tra due interi come la seguente.

Inoltre nel computer Hack necessitiamo di un unico circuito per effettuare sia la somma che la sottrazione in quanto i due numeri forniti in input alla ALU sono sempre in **complemento a 2**, e come abbiamo visto in precedenza la sottrazione tra due numeri in complemento a 2 si effettua facendo la somma bit a bit.

### ▼ 6.2 - Organizzazione delle memorie

## Gerarchia delle memorie

Finora abbiamo visto solo memorie realizzate utilizzando flip-flop, le quali sono le più veloci ma anche le più costose. Non è dunque possibile realizzare un'intera memoria con tale tecnologia, per via dei costi e delle dimensioni, per questo la memoria all'interno di un'elaboratore viene organizzata seguendo una gerarchia (dalla più veloce e più costosa alla meno veloce e meno costosa):

- 1. SRAM (Static), usate per la cache e per i registri.

- 2. DRAM (Dynamic), usate per la memoria centrale.

- 3. **Dischi**, usate come memorie secondarie.

Siccome i vari livelli di memoria devono comunicare tra loro si utilizzano sofisticati algoritmi di caching e paginazione per il passaggio dei dati.

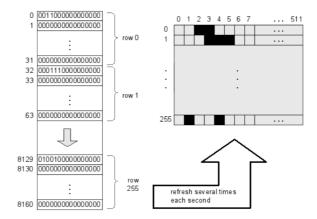

## **SRAM e DRAM**

Mentre la realizzazione delle **SRAM** l'abbiamo vista in precedenza nella sezione "Circuiti sequenziali", le **DRAM**, usate per realizzare le memorie centrali, sono composte da **un solo transistor** e un **condensatore** che mantiene, tramite carica elettrica, un singolo bit. Per questo motivo, visto che il condensatore perde la sua carica, deve essere frequentemente ricaricato per evitare di perdere la propria informazione. Vengono dunque svolte periodiche fasi di **refresh**, ad intervalli dell'ordine del millisecondo, e questo causa una maggiore **lentezza** rispetto alle SRAM. Nonostante ciò, per via del fatto che sono costituite da un solo transistor, **costano meno** e sono più piccole.

### Cache

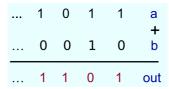

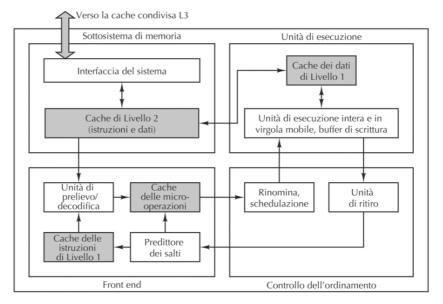

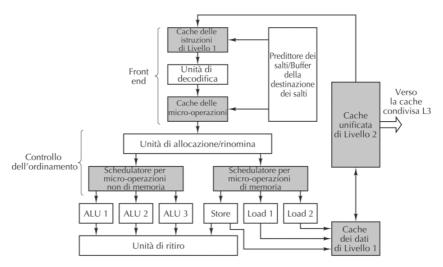

Le **memorie cache**, utilizzare per aumentare la velocità di accesso alle informazioni in memoria, sono organizzate in modo sofisticato. Esistono diverse tipologie di cache, riportiamo un esempio di **cache a 3 livelli** largamente utilizzato:

- 1. Cache di primo livello: direttamente nel chip della CPU separata fra istruzioni e dati (tra i 16 e i 64 KB).

- 2. Cache di secondo livello: nello stesso involucro della CPU unificata alle istruzioni e dati (tra 512 KB e 1 MB).

### 3. Cache di terzo livello: esterna alla CPU (alcuni MB).

Ogni memoria cache lavora seguendo due principi, i quali la rendono utile ed efficace:

#### Località temporale

Indica l'alta probabilità che una **stessa cella** venga acceduta più volte a breve distanza di tempo. Per questo motivo mantenendo in cache una cella acceduta di recente aumenta la probabilità che nelle prossime operazioni sia necessario riaccedere alla medesima cella senza dover passare per la memoria centrale.

Ad esempio ritroviamo la località temporale quando si lavora con degli stack (last-in-first-out) o con dei loop.

### Località spaziale

Indica l'alta probabilità che **celle di memoria vicine** vengano accedute a breve distanza di tempo. Per questo motivo mantenendo in cache blocchi contigui di celle aumenta la probabilità che nelle prossime operazioni vengano accedute altre celle che si trovano già in cache, senza dover passare per la memoria centrale.

Ad esempio ritroviamo la località spaziale quando si attua un'esecuzione sequenziale delle istruzioni o un accesso sequenziale ad un array.

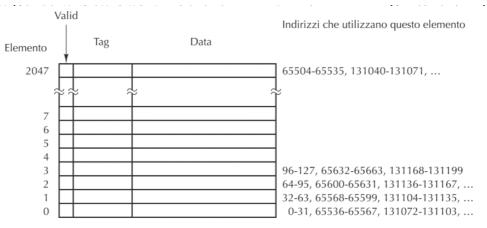

A livello di microarchitettura si definisce il modo di organizzare la cache. Esistono infatti diverse modalità di gestione di una cache, noi vedremo come esempio la **direct mapped cache** (cache a corrispondenza diretta).

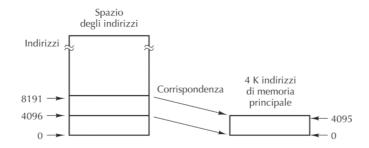

Si divide la memoria centrale in blocchi di memoria di dimensione **m**. La cache è invece organizzata in un numero **n** di linee di cache di dimensione m. I blocchi in memoria centrale di dimensione m possono dunque essere inseriti in cache utilizzando uno schema detto "**ad orologio**", ovvero il **k**-esimo blocco in memoria centrale viene inserito nella linea di cache con indice **k** % **n**. In questo modo, ad ogni accesso in memoria, in base all'indirizzo della cella di memoria, si capisce in quale linea di cache cercarlo.

#### Esempio:

Prendiamo come esempio una direct mapped cache con 2048 linee (n) di dimensione 32 byte (m).

Direct mapped cache con 2048 linee di dimensione 32 byte.

Ogni linea della cache presenta i seguenti dati:

- Valid: indica se la linea di cache contiene un blocco.

- Tag: indica quale linea di cache è contenuta.

- Data: indica il contenuto di 32 byte del blocco.

Avendo indirizzi con un certo numero di bit per indirizzare celle della memoria centrale occorre prendere un numero di bit meno significativi al fine di poter prendere il giusto byte dentro data. Il successivo numero di bit viene preso al fine di indicare la giusta linea di cache nella quale andare a cercare. Il restante numero di bit, quelli più significativi, viene utilizzato per controllare se coincidono con il contenuto del tag della linea in questione; se il tag non è uguale o valid è falso occorre andare a cercare in memoria centrale.

Un esempio con indirizzi a 32 bit è il seguente:

- $\circ$  I primi **5 bit meno significativi** vengono utilizzati per prendere il giusto byte nel contenuto di data, poichè  $2^5=32$ .

- $\circ$  I **successivi 11 bit** vengono utilizzati per capire quale linea della cache utilizzare, poichè  $2^{11}=2048$ .

- I **restanti 16 bit** più significativi vengono utilizzati per verificare, sempre se valid è vero, che siano uguali a quelli del contenuto di tag.

| Tag (16 bit)                                       | Linea (11 bit)       | Data (11 bit) |

|----------------------------------------------------|----------------------|---------------|

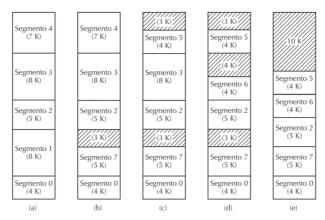

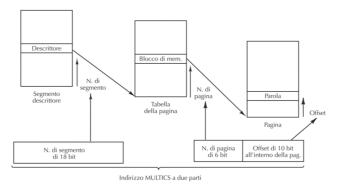

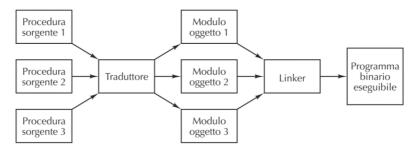

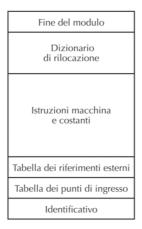

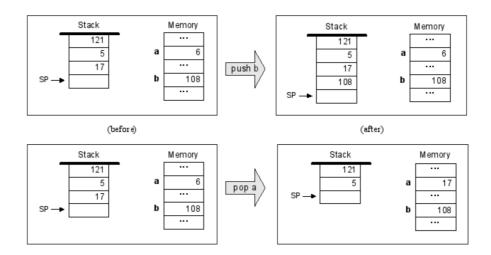

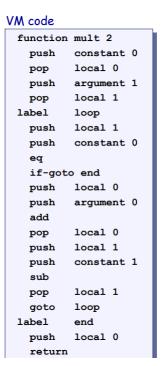

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 | 14 13 12 11 10 9 8 7 | 6543210       |